LA 1 Modul 4: Percobaan 1

1. Jurnal[Kembali]

2. Alat dan Bahan[Kembali]

a. Panel DL 3303D

b. Panel DL 2203C

c. Panel DL 2203S

d. Jumper

e. JK flip-flop

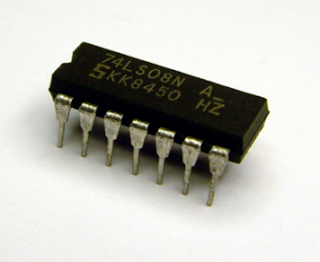

f. Gerbang AND

g. Switch SPDT

h. Power DC

i. Clock

j. LED

3. Rangkaian[Kembali]

4. Prinsip kerja[Kembali]

Pada percobaan 1, digunakan 4 JK flip-flop yang kaki clk nya dihubungkan ke gerbang AND. Pada kondisi pertama, inputan B3-B6 = 0, B0 & B2 = 1, dan B1 = X sehingga output yang didapatkan pada rangkaian dalah SISO (Serial In Serial Out). Pada kondisi ini RS menjadi nonaktif dan gerbang AND mengeluarkan output clock yang dihubungkan ke inputan JK flip-flop selanjutnya. Saat clock rise time, maka data akan masuk secara satu persatu dan bergeser dari kanan ke kiri yang menandakan shift register SISO.

Pada kondisi kedua, inputan B3-B6 = 0, BI = don’t care, B0 = 1, B2 = ↓. B2 merupakan inputan clock sebelum gerbang AND. Sat B2 berlogika 1 maka clock akan berubah-ubah (dari 1-0, 0-1). Pada saat ini data akan masuk secara satu-persatu, kemudian saat B2 berlogika 0 data terhenti karena output dari gerbang AND adalah 0. Pada saat itu data pada output keluar secara serentak yang menandakakan bahwa rangkaian tersebut adalah rangkaian shift register SIPO (Serial In Serial Out).

Pada kondisi ketiga, diberikan B3-B6 = X, B1 = 0, dan B0 & B2 = 1. Pada kondisi ini inputan B3-B6 masing-masing berperan sebagai inputan data pada shift register. Input J berlogika 1 dan gerbang AND akan aktif dengan output clock. Data yang masuk pada input S tiap-tiap JK flip-flop terhubung ke B3-B6 sehingga dta akan mauk secara parallel. Karena adanya input clock maka saat rise time data akan berpindah/bergeser keluar satu- persatu. Sehingga dapat dikatakan rangkaian tersebut adalah rangkaian shift register PISO (Paralle In Serial Out).

Pada kondisi keempat, diberikan input B3-B6 = X, BO = 1, dan B1 & B2 = 0. Pada kondisi ini inputan J tidak aktif sehingga tidak ada perubahan clock. Data dimasukkan melalui input set masing-masing JK flip-flop (B3-B6) dan data akan masuk secara serentak dan juka akan keluar secara serentak karena tidak ada clock. Dapat dikatakan rangkaian tersebut adalah rangkaian shift register PIPO (Parallel In Parallel Out).

5. Video percobaan[Kembali]

6. Analisa[Kembali]

a. Analisa output yang dihsilkan tiap-tiap kondisi

· Pada kondisi, diberkan inputan B3-B6 = 0, B0 & B2 = 1, dan B1

= X sehingga output yang didapatkan pada rangkaian dalah SISO (Serial In Serial

Out). Pada kondisi ini RS menjadi nonaktif dan gerbang AND mengeluarkan output

clock yang dihubungkan ke inputan JK flip-flop

selanjutnya. Saat clock rise time, maka data akan masuk secara satu

persatu dan bergeser dari kanan ke kiri yang menandakan shift register SISO.

· Pada kondisi 2, inputan B3-B6 = 0, BI = don’t care, B0 = 1, B2 = ↓.

B2 merupakan inputan clock sebelum gerbang AND. Sat B2 berlogika 1 maka clock

akan berubah-ubah (dari 1-0, 0-1). Pada saat ini data akan masuk secara satu-persatu,

kemudian saat B2 berlogika 0 data terhenti karena output dari gerbang AND adalah

0. Pada saat itu data pada output keluar secara serentak yang menandakakan

bahwa rangkaian tersebut adalah rangkaian shift register SIPO (Serial In Serial

Out)

· Pada kondisi 3, diberikan B3-B6 = X, B1 = 0, dan B0 & B2 = 1.

Pada kondisi ini inputan B3-B6 masing-masing berperan sebagai inputan data pada

shift register. Input J berlogika 1 dan gerbang AND akan aktif dengan output clock. Data yang masuk pada input S tiap-tiap JK

flip-flop terhubung ke B3-B6 sehingga dta akan mauk secara parallel. Karena adanya

input clock maka saat rise time data akan berpindah/bergeser keluar satu-

persatu. Sehingga dapat dikatakan rangkaian tersebut adalah rangkaian shift

register PISO (Paralle In Serial Out).

· Pada kondisi 4, dberikan input B3-B6 = X, BO = 1, dan B1 & B2

= 0. Pada kondisi ini inputan J tidak aktif sehingga tidak ada perubahan clock.

Data dimasukkan melalui input set masing-masing JK flip-flop (B3-B6) dan data akan

masuk secara serentak dan juka akan keluar secara serentak karena tidak ada

clock. Dapat dikatakan rangkaian tersebut adalah rangkaian shift register PIPO (Parallel

In Parallel Out).

b. Jika gerbang

AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip-flop

bandingkan output yang didapatkan.

Jika

gerbang AND dihapus, maka output yang didapatkan pad atiap kondisi menjadi SISO

(Serial In Serial Out) karena clock yang di inputkan stabil.

7. Link download[Kembali]

HTML [download]

Video [download]

Datasheet [download]

Tidak ada komentar:

Posting Komentar