LA 2 Modul II: Percobaan 1

1. Jurnal[Kembali]

2. Alat dan Bahan[Kembali]

a. Jumper

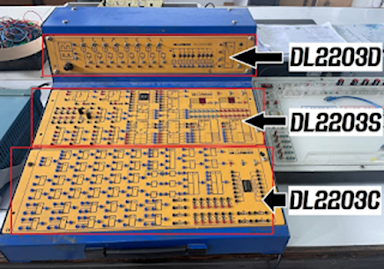

b. Panel DL

2203D

c. Panel DL

2203C

d. Panel DL

2203S

e. IC 7408 (JK

filp flop)

f.

IC 7474 (D flip-flop)

g. Power DC

h. Switch

(SW-SPDT)

i. Logicprobe

3. Rangkaian[Kembali]

4. Prinsip Kerja[Kembali]

Rangkaian pada percobaan 1 ini menggunakan JK flip-flop dan D flip-flop dengan. Untuk inputnya adalah switch dengan 7 saklar yang diberi nama B0 – B6 yang dihubungkan dengan VCC. B0 dihubungkan ke R di kedua flip flop, B1 dihubungkan dengan S di kedua flip flop juga. B2 dihubungkan dengan J pada JK flip flop. B3 dihubungkan dengan CLOCK (yang aktif pada fall time) pada JK flip flop. B4 dihubungkan dengan K pada JK flip flop. B5 dihubungkan dengan D pada D flip flop. B6 dihubungkan dengan CLOCK (yang aktif pada rise time) pada D flip flop. JK flip flop memiliki 2 output yaitu Q dan Q’, begitu juga dengan D flip flop juga memiliki 2 output yaitu Q dan Q’. Setiap output dihubungkan dengan logic probe sebagai penanda adanya keluaran dari masing masing flip flop.

Pada rangkaian divariasikan input dari flip flop dengan mengganti-ganti 7 switch, apakah mati atau hidup. Sesuai dengan table kebenarannya maka output dari masing masing flip flop akan bervariasi juga.

5. Video Percobaan[Kembali]

6. Analisis[Kembali]

a. Bagaimana jika

B0 dan B1 sama-sama diberi logika 0, apa yang terjadi pada rangkaian?

Jika B1 dan B0 sama -sama diberi logika 0, maka output yang dihasilkan, yaitu Q=1 dan Q’=1. Kondisi tersebut disebut kondisi terlarang dimana keadaannya tidak stabil. Nilai output bernilai 1 karena rangkaiannya bersifat active low dimana rangkaian aktif saat input berlogika 0 sehingga outputnya bernilai 1.

b. Bagaimana

jika B3 diputuskan/tidak dihubungkan pada rangkaian, apa yang terjadi pada rangkaian?

Jika B3 diputuskan/tidak dihubungkan maka akan berpengaruh terhadap

JK flip-flop. Hal ini disebabkan yang terhubung ke clock pada JK flip-flop

adalahh B3. Saat input dari J dan K divariasikan maka outputnya tidak akan

mengalami perubahan karena nilai J K flip-flop dipengaruhi oleh clock. Namun,

nilai JK flip-flopdipengruhi pda nilai set dan reset sesuai dengan sifat inputnya,

yaitu active low. Sehingga jika input=1, maka output=0 dan jika input=1 maka output=0.

Untuk rangkaian D flip-flop tidak berpengaruh karena clocknya masih ada.

c. Jelaskan apa

yang dimaksud dengan kondisi toggle, kondisi not change, dan kondisi terlarang

pada flip-flop

· Kondisi toggle merupakan kondisi yang terjadi saat input J dan K

bernilai 1, dimana nilai input J=1 dan K=1. Maka outputnya akan

berubah-ubahyang disebut dengan kondisi toggle. Contoh kondisi toggle adalah saat

output Q=1 dan Q’=0 maka pada togglenya akan berlaku pergantian, sehingga

outputnya menjadi Q=0 dan Q’=1.

· Kondisi not change merupakan kondisi dimana flip-flop akan

mempertahankan kondisi sebelumnya atau tidak mengalami perubahan. Contohnya

saat output Q=1 dan Q’=0 maka pada kondisi not change outputnya menjadi Q=1 dan

Q’=0. Kondisi ini terjadi ketika input sama-sama berlogika 0 dan outputnya akan

sam dengan output sebelumnya.

· Kondisi terlarang merupakan kondisi yang terjadi jika utput yang

dhasilkan sama-sama 1. Kondisi ini disebut kondisi terlarang karena nilai Q dan

Q’ seharusnya berlawanan. Kondisi ini sebaiknya dihindari karena dapat merusak

alat.

7. Download[Kembali]

HTML [download]

Rangkaian [download]

Video [download]

Datasheet [download]

Tidak ada komentar:

Posting Komentar